〈2〉遅れをとった技術戦略──取り残された日本の技術者

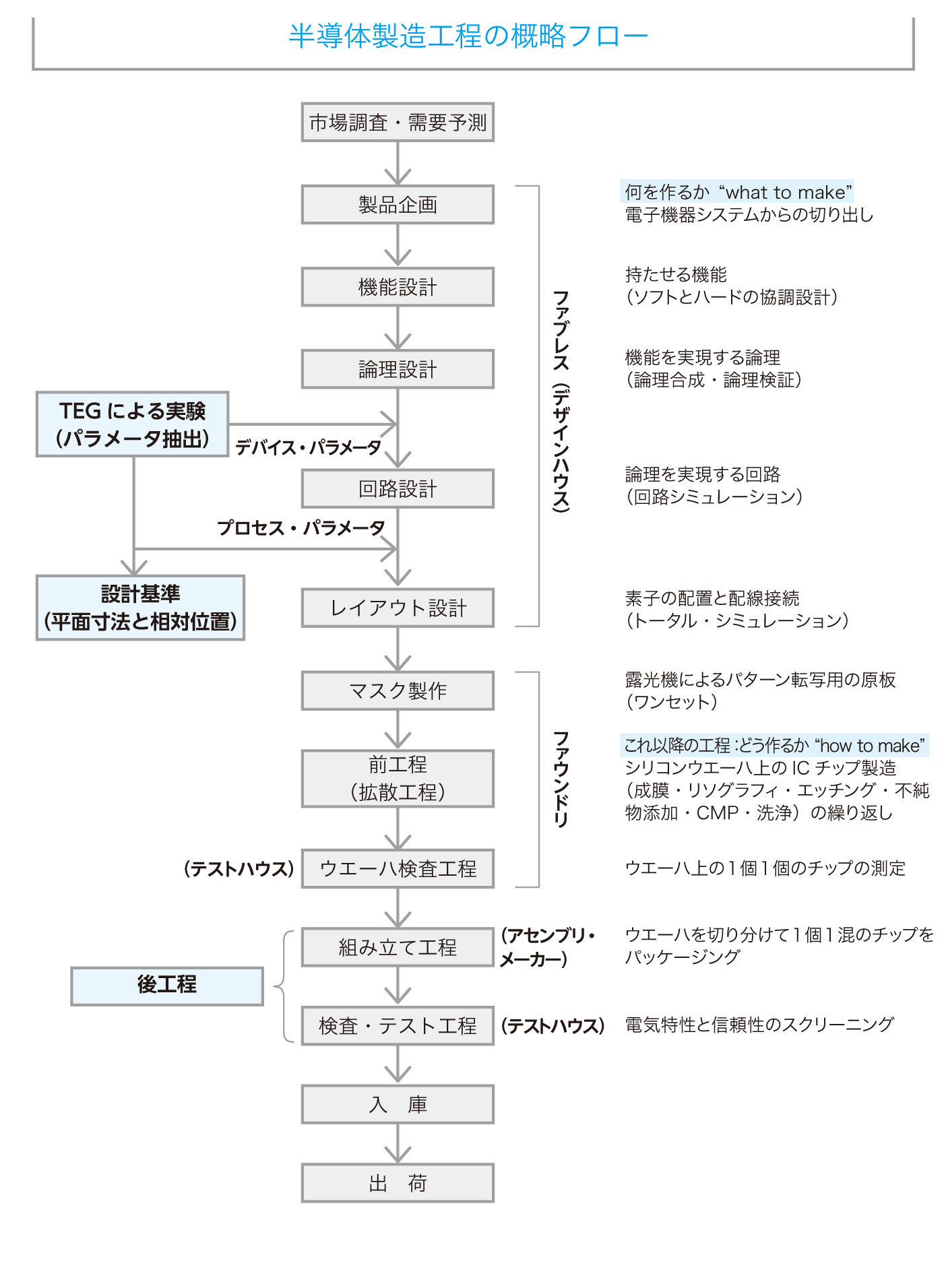

第二の問題として、半導体の設計におけるEDAツールの問題があります。1980年代の後半から1990年代に入ると、半導体の設計はCAD(コンピュータ支援設計)をフルに活用して、図に示したように、

機能設計 → 論理設計 → 回路設計 → レイアウト設計

という階層的なトップダウン設計が広く利用されるようになりました。特にロジック系、中でもSOCでは必要不可欠な手法になったのです。これに合わせてケイデンス(Cadence)、シノプシス(Synopsys)、メンター(Mentor)などのEDAベンダーが存在感を増してきました。

TEG:Test Element Group の略。半導体の設計、プロセス、製造、信頼性を検討・評価するための素子、あるいはそのためのマスク。

一方で日本の大手半導体メーカーは自社内で開発した独自のEDAツールを持っていたこともあり、もっぱら自社のEDAツールを利用して製品開発を行なっていました。むしろ、「自社EDAツールが会社の強みになる」と考え、社外にはツールを使わせないでクローズドにしておいた方が有利に働く、と考えていた節さえ見られました。

しかし、その結果はどうだったでしょうか。餅は餅屋で、EDAベンダーが供給するツールは世界中の多くの設計者に愛用され、改善を加えられつつ標準化が進むのと同時に、それで設計した利用分野ごとの優れた数多くのIPを生み出していったのです。

いっぽう、自社のEDAツールに固執していた日本メーカーはEDA技術の急速な進歩に遅れを取り、またそれで設計したIPは汎用性を失うだけではなく、外部の優れたIPを簡単には利用できなくなるという、遅れた開発環境に取り残されていきました。

これが日本の半導体メーカーが1990年代以降、ロジック系の製品で大きく躍進できなかった一因になっていると思われます。