Photo:Narumon Bowonkitwanchai/gettyimages

Photo:Narumon Bowonkitwanchai/gettyimages

半導体の性能を高める方法として、半導体の回路線幅の「微細化」があるが、近年はその難易度が急激に上がっている。そこで注目を集めているのがチップの組み立て(パッケージング)によって性能の向上を図る方法だ。中でも「チップレット」集積と呼ばれる手法では、日本に光る技術を持った企業が多い。特集『半導体 投資列島』(全9回)の#3では、投資の観点から、チップレットなど後工程での“最強技術”を持った日本企業11社を厳選して紹介する。(丸三証券アナリスト 皆川明伽)

インテルもつまずいた“微細化”に頼らない

歩留まりを改善する手法「チップレット」

半導体高性能化の“新トレンド”が、技術に強い日本の「後工程」企業に一大ビジネスチャンスをもたらしている。

半導体チップの性能向上の歴史は、集積回路の線幅をより細くしていく「微細化」の歴史といえる。回路線幅が微細になれば、チップに集積できる回路の大規模化が可能だ。これによって半導体の性能が高まり、電力消費も抑えられる。さらにチップの小型化によって、製造コストも低減される。

ところが近年は、微細化が高度化したために、製造時の歩留まりを高めることが難しくなってきた。先端半導体での歩留まり悪化は、製造コストの増大をもたらす。チップを作ることができても、コストを製品価格に転嫁せざるを得ず、結果的にビジネス化が困難になるケースが目立つようになった。

それを象徴する出来事が、半導体メーカーで世界トップの米インテルが、10ナノメートル(ナノは10億分の1)プロセスの開発・量産計画で大幅に遅れてしまったことだ。同社は2016年から10ナノメートルプロセスの量産に入る計画を組んでいたが、実際の量産化は18年とかなり遅れた。

インテルの計画が遅れた要因の一つは、チップの単位面積当たりのトランジスタ(半導体の性能を上げる鍵になる)の数を増やすことができなかった点にあるといわれる。つまり、微細化でつまずいたのである。

そこで近年、ウエハーを半導体チップとして切り出して、IC(集積回路)やLSI(高密度集積回路)として組み立てる(パッケージング)際の工夫によって、高性能化を図る手法の研究開発と導入が進んだ。

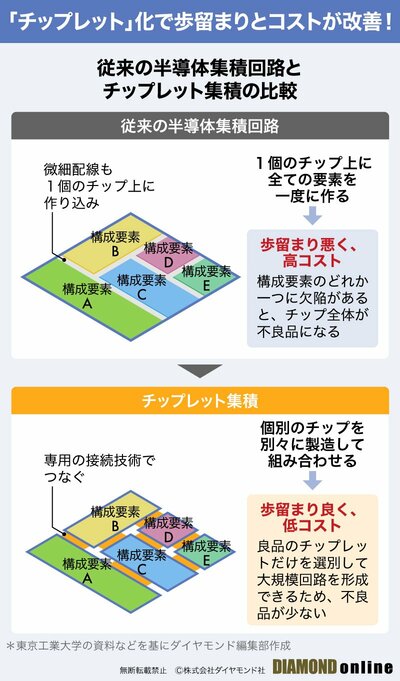

いま、半導体業界が最も注目している手法が「チップレット」集積である。これは従来のように大規模な回路を“一つのチップ”としていっぺんにまとめて作る手法とは異なり、まず、複数の小さなチップ(チップレット)を作り、チップレット同士をつなぐことで大規模回路を作る技術である。

半導体の性能を上げるためにチップの面積を増やそうとした場合、一つの大規模回路では、ごく一部に不具合が生じてもチップ全体が不良品となってしまう。一方、チップレット集積で大規模回路を形成する方法なら、不具合のないチップレットのみを組み合わせて使うことで、個々のチップレットだけでなく、チップ全体の歩留まりが高まる。つまり、パッケージングのノウハウで、高性能化とコストダウンの両立を図ろうというわけだ。

チップレット集積には、「SiP(システム・イン・パッケージ)」と呼ばれる複数チップや素子を一つのパッケージにまとめる方法のほか、複数チップを実装する際に大きな接続用のチップを介して接続する「2.5次元実装」や、チップを縦方向に立体的に積み重ねて接続する「3次元実装」など、さまざまな形がある。

ただし、チップレットなど先進パッケージングには、後工程での高い技術力が必要不可欠だ。そして、この分野で光る技術を持つメーカーが多数ひしめいているのが日本である。

次ページでは、チップレット集積など先進パッケージングで不可欠な技術を持つ日本企業11社について、それぞれ強みとなるポイントと共に、今期と来期の予想増益率、予想PER(株価収益率)を銘柄表にまとめて一挙紹介する。